гЂЬиЖћ10ФЩУзжЦГЬЕФзюаЁеЄМЋМфОрДг70ФЩУзЫѕаЁжС54ФЩУз,ЧвзюаЁН№ЪєМфОрДг52ФЩУзЫѕаЁжС36ФЩУзЁЃГпДчЕФЫѕаЁЪЙЕУТпМОЇЬхЙмУмЖШПЩДяЕНУПЦНЗНКСУз1.008вкИіОЇЬхЙм,ЪЧжЎЧА...

гЂЬиЖћ10ФЩУзжЦГЬЕФзюаЁеЄМЋМфОрДг70ФЩУзЫѕаЁжС54ФЩУз,ЧвзюаЁН№ЪєМфОрДг52ФЩУзЫѕаЁжС36ФЩУзЁЃГпДчЕФЫѕаЁЪЙЕУТпМОЇЬхЙмУмЖШПЩДяЕНУПЦНЗНКСУз1.008вкИіОЇЬхЙм,ЪЧжЎЧА...

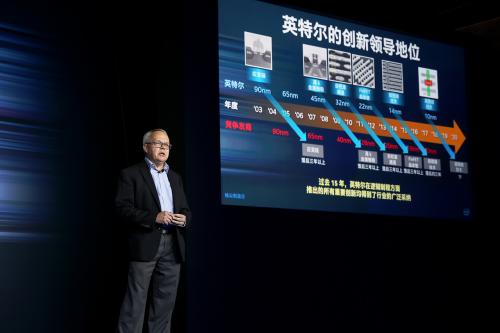

гЂЬиЖћзёбФІЖћЖЈТЩЃЌГжајЯђЧАЭЦНјжЦГЬЙЄвеЃЌУПвЛИіНкЕуОЇЬхЙмЪ§СПЛсдіМгвЛБЖЃЌ14nmКЭ10nmЖМзіЕНСЫЃЌВЂДјРДИќЧПЕФЙІФмКЭадФмЁЂИќИпЕФФмаЇЃЌЖјЧвОЇЬхЙмГЩБОЯТНЕЗљЖШЧАЫљЮДгаЁЃ...

гЂЬиЖћзёбФІЖћЖЈТЩЃЌГжајЯђЧАЭЦНјжЦГЬЙЄвеЃЌУПвЛИіНкЕуОЇЬхЙмЪ§СПЛсдіМгвЛБЖЃЌ14nmКЭ10nmЖМзіЕНСЫЃЌВЂДјРДИќЧПЕФЙІФмКЭадФмЁЂИќИпЕФФмаЇЃЌЖјЧвОЇЬхЙмГЩБОЯТНЕЗљЖШЧАЫљЮДгаЁЃ...

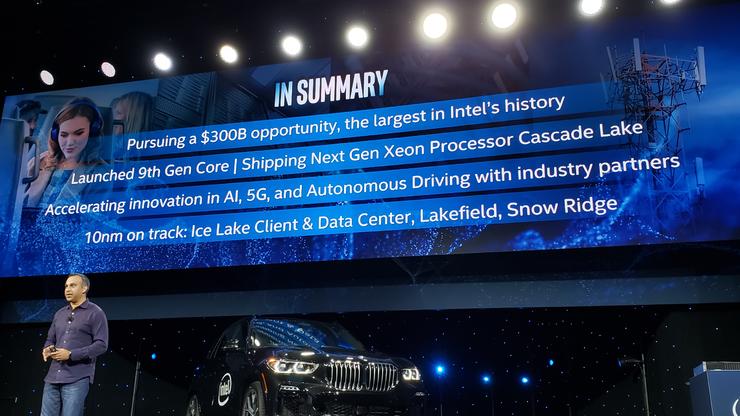

ЁАгЂЬиЖћОЋМтжЦдьШеЁБЛюЖЏНёЬьОйааЃЌеЙЪОСЫгЂЬиЖћжЦГЬЙЄвеЕФЖрЯюживЊНјеЙЃЌАќРЈЃКгЂЬиЖћ10ФЩУзжЦГЬЙІКФКЭадФмЕФзюаТЯИНкЃЌгЂЬиЖћЪзПю10ФЩУзFPGAЕФМЦЛЎЃЌВЂаћВМСЫвЕФкЪзПюУцЯђ...

ЁАгЂЬиЖћОЋМтжЦдьШеЁБЛюЖЏНёЬьОйааЃЌеЙЪОСЫгЂЬиЖћжЦГЬЙЄвеЕФЖрЯюживЊНјеЙЃЌАќРЈЃКгЂЬиЖћ10ФЩУзжЦГЬЙІКФКЭадФмЕФзюаТЯИНкЃЌгЂЬиЖћЪзПю10ФЩУзFPGAЕФМЦЛЎЃЌВЂаћВМСЫвЕФкЪзПюУцЯђ...

2018ФъЕФгЂЬиЖћЖШЙ§СЫЫќ50ЫъЕФЩњШеЃЌЭЌЪБвВдкетвЛФъИјГдЙЯШКжкдьСЫВЛЩйСЯЁЃНёЬьЮвУЧжиЕуРДПДПДЃЌетМв50ФъРДвЛжБв§СьПЦШЋЧђПЦММЕФЦѓвЕЃЌШчКЮдкЕБНёИќЮЊМЄСвЕФОКељЛЗОГжаБЃГжДД...

2018ФъЕФгЂЬиЖћЖШЙ§СЫЫќ50ЫъЕФЩњШеЃЌЭЌЪБвВдкетвЛФъИјГдЙЯШКжкдьСЫВЛЩйСЯЁЃНёЬьЮвУЧжиЕуРДПДПДЃЌетМв50ФъРДвЛжБв§СьПЦШЋЧђПЦММЕФЦѓвЕЃЌШчКЮдкЕБНёИќЮЊМЄСвЕФОКељЛЗОГжаБЃГжДД...

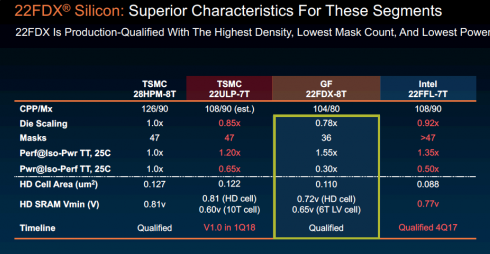

дкжаЙњНЈГЇгыЭЖзЪFDЃSOIЃЈШЋКФОЁОјдЕВуЩЯЙшЃЉЙЄвеЃЌЛђаэЪЧИёаОЃЈGlobalFoundriesЃЉCEO Sanjay JhaжАвЕЩњбФзюживЊЕФЖФзЂЃЌЦкЭћЭЈЙ§етСНЯюОйДыИјОЇ...

дкжаЙњНЈГЇгыЭЖзЪFDЃSOIЃЈШЋКФОЁОјдЕВуЩЯЙшЃЉЙЄвеЃЌЛђаэЪЧИёаОЃЈGlobalFoundriesЃЉCEO Sanjay JhaжАвЕЩњбФзюживЊЕФЖФзЂЃЌЦкЭћЭЈЙ§етСНЯюОйДыИјОЇ...

НќШеЃЌгЂЬиЖћгыСЊЗЂПЦе§ЪНаћВМеНТдКЯзїЙиЯЕЃЌвВМДЮДРДСЊЗЂПЦЕФВПЗжаОЦЌНЋгЩгЂЬиЖћДњЙЄЁЃЮЊДЫЃЌгЂЬиЖћИФНј22FFLНкЕуЃЌДђдьГіаТЕФIntel 16nmжЦГЬЁЃСЊЗЂПЦНЋЪЙгУгЂЬиЖћЕФ...

гЂЬиЖћЭЦГіЕкЖўДњЕЭЮТПижЦаОЦЌHorse Ridge IIЃЌетБъжОзХгЂЬиЖћдкЭЛЦЦСПзгМЦЫуПЩРЉеЙадЗНУцШЁЕУгжвЛИіРяГЬБЎЁЃ

гЂЬиЖћЭЦГіЕкЖўДњЕЭЮТПижЦаОЦЌHorse Ridge IIЃЌетБъжОзХгЂЬиЖћдкЭЛЦЦСПзгМЦЫуПЩРЉеЙадЗНУцШЁЕУгжвЛИіРяГЬБЎЁЃ

МЋаЁГпДчЯТЃЌаОЦЌЮяРэЦПОБдНРДдНФбвдПЫЗўЃЌЕЋУПЕНЙиМќЪБПЬЃЌзмгааТММЪѕНЋПДЫЦзпЯђжеЕуЕФФІЖћЖЈТЩЭЦвЛАбЃЌЖјаЁаОЦЌе§дкНЋаОЦЌадФмНјЛЏв§ЯђИќОпОМУаЇвцЕФЮДРДЁЃ

ЭтНчЫЦвбВњЩњВЛЩйжЪвЩЁЃвЛЯђвдМмЙЙКЭЙЄвебяУћСЂЭђЕФIntelЃЌЫЦКѕдкздМКзюФУЪжЕФСьгђгааЉholdВЛзЁЃЌгжБЛЦфЫћСьгђеМОнаэЖрОЋСІЁЃ

ЭтНчЫЦвбВњЩњВЛЩйжЪвЩЁЃвЛЯђвдМмЙЙКЭЙЄвебяУћСЂЭђЕФIntelЃЌЫЦКѕдкздМКзюФУЪжЕФСьгђгааЉholdВЛзЁЃЌгжБЛЦфЫћСьгђеМОнаэЖрОЋСІЁЃ

гЂЬиЖћБЛЪРШЫЪьжЊЕФЪЧCPUЃЌДцДЂЃЌЛЙгаНќФъРДЪеЙКЕФFPGAЁЂЕЋЦфЪЕдкGPUЗНУцЃЌвВгаВЛДэЕФБэЯжЁЃ

гЂЬиЖћБЛЪРШЫЪьжЊЕФЪЧCPUЃЌДцДЂЃЌЛЙгаНќФъРДЪеЙКЕФFPGAЁЂЕЋЦфЪЕдкGPUЗНУцЃЌвВгаВЛДэЕФБэЯжЁЃ

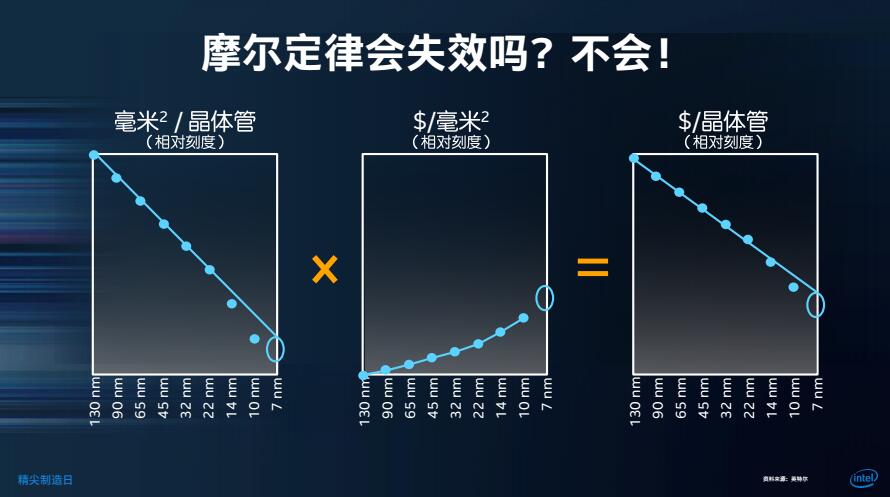

АыИіЪРМЭЧАЃЌгЂЬиЖћДДЪМШЫжЎвЛИъЕЧЁЄФІЖћЬсГіЁАФІЖћЖЈТЩЁБЃЈMooreЃЇs LawЃЉЃЌДгетвдКѓЃЌаОЦЌГЇЩЬУЧЖрзёДгетвЛЖЈТЩЩњВњаОЦЌЁЃЖјНќФъРДЃЌЁАФІЖћЖЈТЩЁББЛЦфЫћГЇЩЬГЊЫЅЃЌБОИУЪЧ...

АыИіЪРМЭЧАЃЌгЂЬиЖћДДЪМШЫжЎвЛИъЕЧЁЄФІЖћЬсГіЁАФІЖћЖЈТЩЁБЃЈMooreЃЇs LawЃЉЃЌДгетвдКѓЃЌаОЦЌГЇЩЬУЧЖрзёДгетвЛЖЈТЩЩњВњаОЦЌЁЃЖјНќФъРДЃЌЁАФІЖћЖЈТЩЁББЛЦфЫћГЇЩЬГЊЫЅЃЌБОИУЪЧ...

НќФъРДЃЌЁАФІЖћЖЈТЩЁББЛЦфЫћГЇЩЬГЊЫЅЃЌБОИУЪЧаОЦЌЁАБЧзцЁБЕФгЂЬиЖћвВдкММЪѕЩЯНЅНЅТфКѓгкОКељЖдЪжЁЃдкДЫДЮЕФМмЙЙШеЃЌгЂЬиЖћеЙЪОСЫЫћУЧЕФжкЖрЯТвЛДњММЪѕКЭвбОзіГіЕФДДаТЃЌЦфжаОЭАќРЈвЕ...

НќФъРДЃЌЁАФІЖћЖЈТЩЁББЛЦфЫћГЇЩЬГЊЫЅЃЌБОИУЪЧаОЦЌЁАБЧзцЁБЕФгЂЬиЖћвВдкММЪѕЩЯНЅНЅТфКѓгкОКељЖдЪжЁЃдкДЫДЮЕФМмЙЙШеЃЌгЂЬиЖћеЙЪОСЫЫћУЧЕФжкЖрЯТвЛДњММЪѕКЭвбОзіГіЕФДДаТЃЌЦфжаОЭАќРЈвЕ...

ФПЧАЪаУцЩЯЪЙгУЕФаОЦЌДѓЖржЛЪЧ10nmжЦГЬЃЌЖјдкИќаЁЕФжЦГЬжаЃЌвбОгжЯЦЦ№СЫвЛЗЌаШЗчбЊгъЁЃгЩгкжЦГЬВЛЖЯЮЂЫѕЃЌДЋЭГЕФЮЂгАММЪѕвбОДяЕНМЋЯоЃЌЮоЗЈНтОіИќОЋУмЕФЦиЙтЯдЯёашЧѓЃЌжЛгаИФгУ...

ФПЧАЪаУцЩЯЪЙгУЕФаОЦЌДѓЖржЛЪЧ10nmжЦГЬЃЌЖјдкИќаЁЕФжЦГЬжаЃЌвбОгжЯЦЦ№СЫвЛЗЌаШЗчбЊгъЁЃгЩгкжЦГЬВЛЖЯЮЂЫѕЃЌДЋЭГЕФЮЂгАММЪѕвбОДяЕНМЋЯоЃЌЮоЗЈНтОіИќОЋУмЕФЦиЙтЯдЯёашЧѓЃЌжЛгаИФгУ...

ЛиПДАыЕМЬхВњвЕЙ§ШЅМИЪЎФъЗЂеЙРњГЬЃЌгЂЬиЖћЕФЁААджїЁБЕиЮЛЪЧЮугЙжУвЩЕФЃЌетКмДѓГЬЖШЩЯЛљгкгЂЬиЖћГжајВЛЖЯЕФДДаТКЭЖЈвхСЫАыЕМЬхВњвЕЕФЗЂеЙзпЪЦ......

ЛиПДАыЕМЬхВњвЕЙ§ШЅМИЪЎФъЗЂеЙРњГЬЃЌгЂЬиЖћЕФЁААджїЁБЕиЮЛЪЧЮугЙжУвЩЕФЃЌетКмДѓГЬЖШЩЯЛљгкгЂЬиЖћГжајВЛЖЯЕФДДаТКЭЖЈвхСЫАыЕМЬхВњвЕЕФЗЂеЙзпЪЦ......

ЮЊЛ§МЋЯьгІЙЄаХВПЕШЪЎЦпВПУХСЊКЯгЁЗЂЕФЁЖЁАЛњЦїШЫ+ЁБгІгУааЖЏЪЕЪЉЗНАИЁЗЃЌЭЦЖЏЁАЛњЦїШЫ+ ...

ЮФЕЕРДдДЃКРћдЊКр