НтЖСЃКICЗтзАаавЕЕФзюаТММЪѕКЭЪаГЁЧїЪЦ

SiPММЪѕЕФгХЪЦдкгк:

ШкКЯЖржжММЪѕ

ФмЙЛдквЛИіЗтзАжаМЏГЩЖржжММЪѕКЭзщМў,Р§ШчзщКЯMEMSКЭCMOSЁЃетжжзщКЯЖдгкДЋЭГICЪЧВЛПЩФмЕФЁЃЫфШЛMEMSКЭCMOSЦїМўгааэЖрЯрЫЦжЎДІ,ЕЋвВгавЛаЉЙиМќЧјБ№ЁЃЪзЯШЪЧашвЊвЛжжЗНЗЈНЋИажЊДЋЕнИјMEMSЦїМў,вђЮЊЫќУЧБиаыгыЛЗОГЯрЛЅзїгУ;ЦфДЮ,MEMSЦїМўЕФРЉеЙЗНЪНгыCMOSВЛЭЌЙЄвеЕФРЉеЙЗНЪНВЛЭЌЁЃ

ВЩгУЖржжЙЄве

SiPММЪѕЬсЙЉЕФМЏГЩЖдПЩДЉДїЩшБИЁЂжЧФмЕЦЛђжЧФмМвОгЕШгІгУЬиБ№гаМлжЕ,вђЮЊетаЉВњЦЗЕФПеМфКЭГпДчЗЧГЃживЊЁЃДгЪЕМЪгІгУПД,SiPЩшМЦЗНАИШкКЯСЫОЇдВМЖЗтзА(WLP)ЁЂ2ЃЎ5DЛђ3DНсЙЙЁЂЕЙзАаОЦЌ(flip-chip)ЁЂв§ЯпМќКЯЁЂЗтзАЬхЕўВу(package-on-package)ЕШЙЄве;ЛЙПЩвдЧЖШыЮодДЦїМўЁЂЙВаЮЦСБЮЁЂТЫВЈЦїКЭЬьЯпЁЃ

ЕфаЭIoTЗНАИЕФМИжжSiPЗтзА

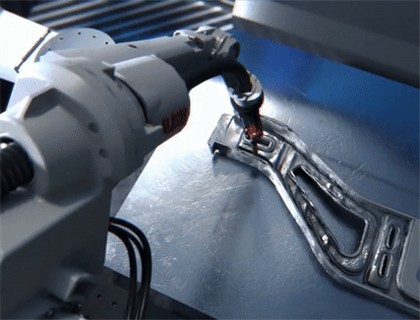

ШкКЯMEMSДЋИаЦї

MEMSДЋИаЦїашвЊгыЛЗОГНЛЛЅвдНјааЩљвєЁЂЙтЛђЦјЬхМьВтЁЃЪЙгУMEMSЗтзАЭЈГЃвЊДгQFNЗтзАЧЈвЦЕНЛљгкВубЙАхЕФЗтзАЁЃВубЙАхЩшМЦПЩвдВЩгУЧЛЛљЗтзАЛђЛьКЯЧЛЗтзА,ЦфжаЗтзАЕФвЛАыЪЧФЃбЙЕФ,СэвЛАыЪЧЮЊMEMSЦїМўЬсЙЉвЛИіПеЧЛЁЃетжжФЃбЙЦїМўИќФмГаЪмЖёСгЕФЛЗОГЁЃ

ЪЕЯжIoTБъзМЛЏЗтзА

ФПЧА,MEMSЁЂДЋИаЦїМАIoTЦїМўЕФЗтзАЩшМЦЛЙКмСуЩЂЁЃЩшМЦШЫдБЯЃЭћЖрИіЯюФПжигУЯрЭЌЕФЗтзА,МДЪЙетаЉЗтзАВЂВЛзмЪЧгыЬиЖЈгІгУМцШнЁЃMEMSЁЂДЋИаЦїЗтзАЕФБъзМЛЏНЋгажњгкНЕЕЭГЩБОКЭМгПьMEMSЕФВЩгУ,діЧПжЦдьЩЬНЋаТВњЦЗЭЦЯђЪаГЁЕФаХаФЁЃ

FOWLPЪЕЯжМЋжТадФм

ФІЖћЖЈТЩдкЙЄвеММЪѕЩЯЫЦКѕвбзпЕНСЫОЁЭЗ,ЫљвдЯШНјЗтзАММЪѕе§дкНгАє,ШчЩШГіОЇдВМЖЗтзА(FOWLP)ОЭПЩвдЬсИпзщМўУмЖШКЭадФм,гажњгкНтОіаОЦЌI/OЯожЦЁЃВЛЙ§,ГЩЙІЕФЙиМќЪЧДгаОЦЌЩшМЦПЊЪМЁЃ

Яждк,FOWLPвбОдквЦЖЏЩшБИЕФХњСПЩњВњжаЪЙгУЁЃЦфЗтзАЙ§ГЬАќРЈНЋЕЅИіаОЦЌАВзАдкГЦЮЊжиЗжВМВу(RDL)ЕФжаМфВуЛљАхЩЯ,ИУВуЬсЙЉаОЦЌжЎМфЕФЛЅСЌвдМАгыI/OКИХЬЕФСЌНг,ЫљгаетаЉаОЦЌЖМЗтзАдквЛИіФЃбЙГЩаЭжаЁЃ

ЫљЮНЩШГіЗтзА,ЪЧНЋСЌНгМўЩШГіЕНаОЦЌБэУц,вдБуЪЕЯжИќЖрЭтВПI/O,ЪЙгУЛЗбѕФЃбЙЛЏКЯЮяЭъШЋЧЖШыЦЌаО(die),вђДЫВЛашвЊОЇдВжВЧђЁЂШлМСЁЂЕЙзАаОЦЌзщзАЁЂЧхЯДЁЂЕзЬюСЯзЂШыКЭЙЬЛЏЕШЙЄвеСїГЬЁЃетЗДЙ§РДгжЯћГ§СЫжаМфВу,ВЂЪЙвьЙЙМЏГЩЕФЪЕЯжИќМгМђЕЅЁЃ

ЩШГіММЪѕПЩвдЬсЙЉБШЦфЫћЗтзАРраЭИќЖрI/OЕФаЁГпДчЗтзАЁЃдчдк2016Фъ,ЦЛЙћОЭЦОНшЬЈЛ§Еч(TSMC)ЕФМЏГЩЩШГі(integrated fan-out,InFO)ОЇдВМЖЗтзАММЪѕ,НЋЦф16nm A10гІгУДІРэЦїгывЦЖЏDRAMМЏГЩЕНiPhone 7ФкВПЕФвЛИіЗтзАжа,ЮЊгІгУДІРэЦїЬсЙЉИќКУЕФШШЙмРэЁЃTSMCЕФInFOЪЙЦЛЙћЪЕЯжСЫЗЧГЃБЁЕФЗтзАЬхЕўВу(PoP,Package-on-Package)ЁЃ

TSMCЕФInFOММЪѕ

InFOЦНЬЈЕФдйЗжВМВуММЪѕНЋЙшЦЌжБНгСЌНгЕНPCBВу,ЖјЮоашСэвЛВуЛљАхЁЃЬЈЛ§ЕчЩшМЦЕФЛЅСЌЭЈПз(TIV)ПЩвдЬсЙЉжЇжљ,ЪЙгУЛьКЯДЙжБКЭЫЎЦНЛЅСЌММЪѕСЌНгВЛЭЌЕФЙшЦЌЛђзщМўЁЃInFOЬхЯжСЫЦфЖЬДЙжБКЭГЄЫЎЦНСЌНгжЎМфЕФСЌНг,МгЫйСЫаХЯЂЕФДЋВЅЁЃ

зїЮЊЖдWLPЕФИФНј,FOWLPММЪѕПЩвдЬсЙЉИќЖргыЙшЦЌаОЕФЭтВПНгЕуЁЃЫќНЋаОЦЌЧЖШыЛЗбѕФЃбЙСЯжа,ШЛКѓдкОЇдВБэУцжЦдьИпУмЖШRDLКЭЮ§Чђ,аЮГЩвЛИіжизщОЇдВЁЃ

ЭЈГЃ,ЫќЪзЯШНЋЧАЕРДІРэЙ§ЕФОЇдВЧаГЩЕЅЖРЕФЦЌаО,ШЛКѓНЋЦЌаОдкдиЬхНсЙЙЩЯИєПЊ,ЦфПеЯЖБЛЬюТњаЮГЩвЛИіжизщОЇдВЁЃFOWLPдкЗтзАКЭгІгУАхжЎМфЬсЙЉСЫДѓСПЕФСЌНгЁЃДЫЭт,ЛљАхЛљБОЩЯБШЦЌаОДѓ,вђДЫЦЌаОМфОрИќЮЊПэЫЩЁЃ

ЗжЯэ

ЗжЯэ

зюаТЛюЖЏИќЖр

-

5дТ8-10ШеСЂМДБЈУћ>> ЙњМЪЮяСїНтОіЗНАИеЙРРЛс

-

5дТ10ШеСЂМДЯТди>> ЁОЪЧЕТПЦММЁПОЋбЁЁЖЦћГЕ SerDes ЗЂЩфЛњВтЪдЁЗАзЦЄЪщ

-

5дТ16ШеЛ№ШШБЈУћ>>> OFweekяЎЕч/АыЕМЬхаавЕЪ§зжЛЏзЊаЭдкЯпбаЬжЛс

-

5дТ28ШеСЂМДЙлПД>> ЁОдкЯпбаЬжЛсЁПAnsysОЕЭЗЕуНКПЩППадММЪѕМАЗНАИ

-

5дТ31ШеСЂМДБЈУћ>> ЁОЯпЯТТлЬГЁПаТЬЦПЦММ2024ЮДРДДДаТЗхЛс

-

8дТ27-29ШеТэЩЯБЈУћ>>> 2024ЃЈЕкЮхНьЃЉШЋЧђЪ§зжОМУВњвЕДѓЛсєпеЙРРЛс

- 1 ДДаТЧ§ЖЏЁЂПЊЗХЙВЯэЁЂЙЄОпИГФмЃЌжњСІЙЄвЕЦѓвЕЙЉгІСДЪ§жЧЛЏзЊаЭЩ§МЖ

- 2 ИГФмаТжЪЩњВњСІ | ИёСІЙЄвЕзАБИаТЦЗЗЂВМЛсдВТњейПЊ

- 3 жЧФмжЦдьжЎТЗЛЙгаЖрдЖЃП

- 4 ЫежндДПиЃКДђдьгХжЪМЦЫуЛњВњЦЗЃЌжњСІЩњВњЩњЛюИпаЇБуНн

- 5 Ansys ЗлФЉ/ПХСЃСїЖрЮяРэЗТецММЪѕНщЩмМААИР§ЭјТчбаЬжЛс4дТ23Шее§ЪНЩЯЯпЃЁ

- 6 ВЉЪРСІЪПРж2023ФъЯњЪлЖюдйДДаТИп Л§МЋгІЖдЮДРДЬєеН

- 7 ЙЄвЕШэМўОоыЂPTCзюДѓЙІГМЭЫСЫ

- 8 ЙЄвЕЩЯТЅДђдьЯжЪЕАцЁАФІЬьЙЄГЇЁБ

- 9 ЁОВЮЛсжИФЯЁП2024аЧЛ№ЩњЬЌДѓЛсбћФњВЮЛсЃЁ

- 10 ИяаТюгН№ГЩаЭЙЄвеЃЌQuintus FlexformвКбЙГЩаЭММЪѕССЯрCCMT2024ЃЌДјРДаавЕаТБфИя

- ИпМЖШэМўЙЄГЬЪІ ЙуЖЋЪЁ/ЩюлкЪа

- здЖЏЛЏИпМЖЙЄГЬЪІ ЙуЖЋЪЁ/ЩюлкЪа

- ЙтЦїМўбаЗЂЙЄГЬЪІ ИЃНЈЪЁ/ИЃжнЪа

- ЯњЪлзмМрЃЈЙтЦїМўЃЉ ББОЉЪа/КЃЕэЧј

- МЄЙтЦїИпМЖЯњЪлОРэ ЩЯКЃЪа/КчПкЧј

- ЙтЦїМўЮяРэЙЄГЬЪІ ББОЉЪа/КЃЕэЧј

- МЄЙтбаЗЂЙЄГЬЪІ ББОЉЪа/В§ЦНЧј

- ММЪѕзЈМв ЙуЖЋЪЁ/НУХЪа

- ЗтзАЙЄГЬЪІ ББОЉЪа/КЃЕэЧј

- НсЙЙЙЄГЬЪІ ЙуЖЋЪЁ/ЩюлкЪа

ЗЂБэЦРТл

ЧыЪфШыЦРТлФкШн...

ЧыЪфШыЦРТл/ЦРТлГЄЖШ6~500Иізж

днЮоЦРТл

днЮоЦРТл