НтЖСЃКICЗтзАаавЕЕФзюаТММЪѕКЭЪаГЁЧїЪЦ

ДЋЭГЖрЦЌаОЗтзАгыFOWLP

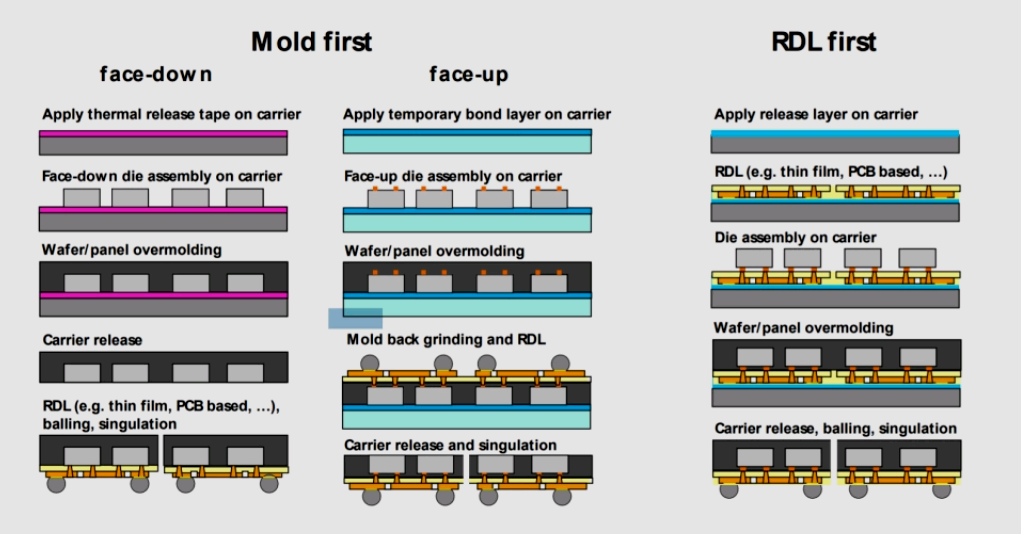

FOWLPгаМИжжБфЬх,УПжжЖМЪЙгУЩдгаВЛЭЌЕФжЦдьВНжшЁЃFOWLPзщМўПЩвдЪЙгУФЃбЙгХЯШ(mold-first)СїГЬДДНЈ,ЦЌаОУцГЏЯТЛђУцГЏЩЯАВзА,ЛђепЪЙгУRDLгХЯШ(RDL-first)зщМўЁЃ

ФЃбЙгХЯШЗНЗЈ

ЦЌаОЪЙгУСйЪБеГКЯВуЛђШШЪЭЗХВуСЌНгЕНдиЬхЩЯ,ШЛКѓНЋЦфФЃжЦЕНЗтзАжаЁЃШчЙћЦЌаОУцГЏЯТАВзА,НгЯТРДЕФВНжшЪЧЪЭЗХСйЪБВу,СЌНгRDL,аЮГЩЭъГЩЗтзАЕФКИЧђЁЃШчЙћЦЌаОУцГЏЩЯАВзА,дђашвЊвЛаЉИНМгВНжшЁЃ

ЪзЯШ,ЕЅИіЦЌаОI/OСЌНгБиаыЭЈЙ§дкЦфЩЯЬэМгЭжљРДРЉеЙ,ШЛКѓдйНјааЖўДЮГЩаЭЁЃГЩаЭКѓ,ЧЖЬѕЕФБГУцБиаыНгЕи,дкСЌНгRDLКЭаЮГЩКИЧђжЎЧАТЖГіжЇжљЁЃ

RDLгХЯШЗНЗЈ

RDLЪЙгУСйЪБЪЭЗХВуСЌНгдиЬх,ЖјЦЌаОСЌНгЕНRDLЁЃШЛКѓЪЧзщзАГЩаЭЁЂдиЬхЪЭЗХЁЂКИЮ§ЧђГЩаЭЁЃетСНжжЗНЗЈЕФзюКѓвЛВНЖМЪЧНЋзщМўЗжПЊ,ЪЙетаЉзщМўећЬхаЮГЩЕЅЖРЕФЦїМўЁЃ

FOWLPММЪѕЕФСНжжЗНЗЈ

етаЉЗНЗЈОпгаВЛЭЌЕФГЩБОКЭадФмШЈКтЁЃдкГЩБОЗНУц,ФЃбЙгХЯШУцГЏЯТЗНЗЈБмУтСЫжЦзїЭжљКЭбаФЅ,вђДЫжЦдьГЩБОНЯЕЭ;зюЪЪКЯЕЭI/OЪ§ЕФгІгУ;ЕЋЪЧ,ДцдкзХЦЌаОвЦЮЛЁЂОЇдВЧЬЧњЕШЮЪЬт,ЯожЦСЫдкИДдгЖраОЦЌЗтзАжаЕФгІгУЁЃ

УцГЏЩЯЕФЗНЗЈМѕЩйСЫетаЉЮЪЬт,ВЂдкШШЙмРэЗНУцгагХЪЦ,вђЮЊаОЦЌБГУцЭъШЋБЉТЖ,гаРћгкЩЂШШЁЃ

дкадФмЗНУц,гыЦфЫћСНжжЗНЗЈЯрБШ,УцГЏЯТЕФЗНЗЈЕФСЌНгТЗОЖИќЖЬЁЃетСНжжЗНЗЈЖМгаЭжљ,ПЩвдНЋСЌНгбгЩьЕНRDL,ЭЌЪБдкаОЦЌЯТгавЛВуВФСЯ,діМгСЫСЌНгжЎМфЕФМФЩњЕчШн,ДгЖјгАЯьСЫЦфИпЦЕадФмЁЃ

2ЃЎ5DЕН3D ICЗтзАЕФЙиМќЪЧTSV

дк2ЃЎ5DЗтзАжа,ЦЌаОВЩгУЖбЕўЛђВЂХХЗХжУдкЛљгкЙшЭЈПз(TSV)ЕФжаМфВуЖЅВПЁЃЕзВПЕФжаМфВуЬсЙЉаОЦЌжЎМфЕФСЌНгЁЃ2ЃЎ5DЗтзАММЪѕЪЧДЋЭГ2D ICЗтзАММЪѕЕФвЛИіНјВН,ЫќЪЙМЃЯпКЭПеМфИќМгОЋЯИЁЃ

2ЃЎ5DЗтзАЭЈГЃгУгкИпЖЫASICЁЂFPGAЁЂGPUКЭФкДцЁЃ2008Фъ,XilinxНЋЦфДѓаЭFPGAЗжГЩСЫЫФИіИќаЁЁЂСМТЪИќИпЕФаОЦЌ,ВЂНЋетаЉаОЦЌСЌНгЕНвЛИіЙшжаМфВуЩЯ,ДгЖјЕЎЩњСЫ2ЃЎ5DЗтзА,зюжеГЩЮЊСїааЕФИпДјПэФкДц(HBM)ДІРэЦїМЏГЩЁЃ

TSVСЌНгЕФЙІФмЭъећЕФ3DЗтзА

дк3D ICЗтзАжа,ТпМЦЌаОЖбЕўдквЛЦ№,ЭЈЙ§ЭTSVдкЙшаОЦЌжЎМфЪЕЯжДЙжБЛЅСЌ,ВЂЪЙгУгадДжаМфВуСЌНгЦЌаОЁЃгыЭЈЙ§ЕМЕчЭЙЕуЛђTSVНЋдЊМўЖбЕўдкжаМфВуЩЯЕФ2ЃЎ5DВЛЭЌ,3D ICЗтзАВЩгУЖрВуЙшОЇдВВЂЭЈЙ§TSVНЋдЊМўЖбЕўдквЛЦ№ЁЃ

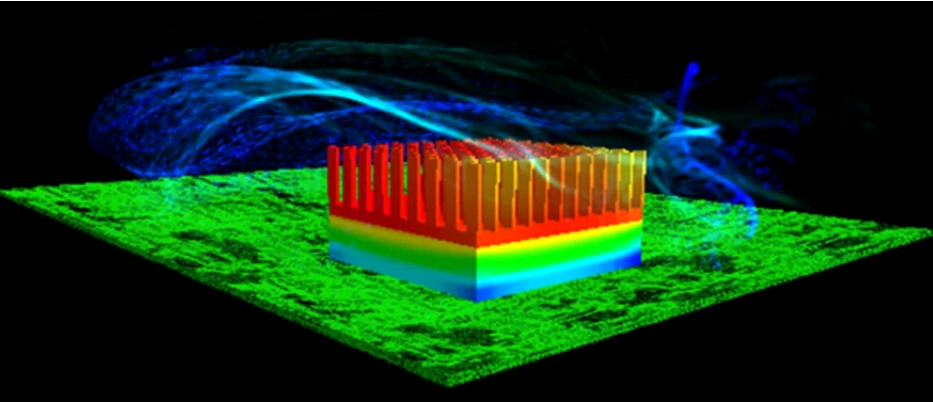

TSVЪЧ2ЃЎ5DКЭ3DЗтзАНтОіЗНАИжаЕФвЛЯюЙиМќММЪѕ,ЫќЬсЙЉСЫвЛжжДЉЙ§ЦЌаОЙшОЇдВЕФДЙжБЛЅСЌЁЃетжжЗтзАЪЧвдОЇдВаЮЪНжЦдьЕФ,РяУцЬюГфСЫЭЁЃTSVЪЧвЛжжДЉЙ§аОЦЌећИіКёЖШЛђЛљАхбгЩьЕФГЄЭЈПзЕчЦјСЌНг,ЫќДДНЈСЫДгаОЦЌвЛВрЕНСэвЛВрЕФзюЖЬТЗОЖЁЃШЛЖј,TSVГ§СЫздЩэЯджјЕФЕчЦјЬиадЭт,ЛЙЖдЦфИННќЕФЦїМўКЭЛЅСЌЕФЕчЦјааЮЊВњЩњМфНггАЯьЁЃ

ЮЊСЫОЋШЗЕиФЃФтвЛИі2ЃЎ5D/3DвьЙЙЯЕЭГ,ЩшМЦепашвЊДгетаЉ2ЃЎ5D/3DдЊЫиЕФЮяРэНсЙЙжаЬсШЁОЋШЗЕчВЮЪ§ЕФЙЄОп,ШЛКѓНЋетаЉВЮЪ§ЪфШыааЮЊЗТецЦїЁЃРћгУЭъећзщМўзАХфЕФ3DЪ§зжТЯЩњФЃаЭ,ЩшМЦепПЩвдзМШЗЕиЬсШЁГі2ЃЎ5DКЭ3DФЃаЭжаЕФМФЩњад,вдЗжЮіадФмКЭЪЪЕБЕФавщзёДгадЁЃ

жЕЕУзЂвтЕФЪЧ,2ЃЎ5DКЭ3DЖбЕўЖМЛсВњЩњИїжжХМШЛЕФЮяРэгІСІ,Р§ШчдкАВзАЙ§ГЬжаЛљАхЧЬЧњКЭХізВв§Ц№ЕФгІСІЁЃЩшМЦШЫдББиаыФмЙЛЗжЮіетжжаОЦЌЗтзАНЛЛЅзїгУв§Ц№ЕФгІСІМАЦфЖдЦїМўадФмЕФгАЯьЁЃвЛЕЉЗтзАНгНќЭъГЩ,ашвЊЕМГіОЋШЗЕФ3DЗтзАШШФЃаЭ,вдБудкЯъЯИЕФPCBКЭШЋЯЕЭГШШЗжЮіжаЪЙгУ,НјЖјЖдЯЕЭГЭтПЧНјаазюжеЕїећ,ВЂгХЛЏздШЛКЭ/ЛђЧПжЦРфШДЁЃ

3D ICЗтзАЕФШШЗТец

ЗжЯэ

ЗжЯэ

зюаТЛюЖЏИќЖр

-

5дТ8-10ШеСЂМДБЈУћ>> ЙњМЪЮяСїНтОіЗНАИеЙРРЛс

-

5дТ10ШеСЂМДЯТди>> ЁОЪЧЕТПЦММЁПОЋбЁЁЖЦћГЕ SerDes ЗЂЩфЛњВтЪдЁЗАзЦЄЪщ

-

5дТ16ШеЛ№ШШБЈУћ>>> OFweekяЎЕч/АыЕМЬхаавЕЪ§зжЛЏзЊаЭдкЯпбаЬжЛс

-

5дТ28ШеСЂМДЙлПД>> ЁОдкЯпбаЬжЛсЁПAnsysОЕЭЗЕуНКПЩППадММЪѕМАЗНАИ

-

5дТ31ШеСЂМДБЈУћ>> ЁОЯпЯТТлЬГЁПаТЬЦПЦММ2024ЮДРДДДаТЗхЛс

-

8дТ27-29ШеТэЩЯБЈУћ>>> 2024ЃЈЕкЮхНьЃЉШЋЧђЪ§зжОМУВњвЕДѓЛсєпеЙРРЛс

- 1 ДДаТЧ§ЖЏЁЂПЊЗХЙВЯэЁЂЙЄОпИГФмЃЌжњСІЙЄвЕЦѓвЕЙЉгІСДЪ§жЧЛЏзЊаЭЩ§МЖ

- 2 ИГФмаТжЪЩњВњСІ | ИёСІЙЄвЕзАБИаТЦЗЗЂВМЛсдВТњейПЊ

- 3 iEiЭўЧПЕчвНСЦЦНАхЕчФдIASO-W10B-N6210

- 4 жЧФмжЦдьжЎТЗЛЙгаЖрдЖЃП

- 5 ЫежндДПиЃКДђдьгХжЪМЦЫуЛњВњЦЗЃЌжњСІЩњВњЩњЛюИпаЇБуНн

- 6 Ansys ЗлФЉ/ПХСЃСїЖрЮяРэЗТецММЪѕНщЩмМААИР§ЭјТчбаЬжЛс4дТ23Шее§ЪНЩЯЯпЃЁ

- 7 ВЉЪРСІЪПРж2023ФъЯњЪлЖюдйДДаТИп Л§МЋгІЖдЮДРДЬєеН

- 8 ЙЄвЕШэМўОоыЂPTCзюДѓЙІГМЭЫСЫ

- 9 ЙЄвЕЩЯТЅДђдьЯжЪЕАцЁАФІЬьЙЄГЇЁБ

- 10 ЁОВЮЛсжИФЯЁП2024аЧЛ№ЩњЬЌДѓЛсбћФњВЮЛсЃЁ

- ИпМЖШэМўЙЄГЬЪІ ЙуЖЋЪЁ/ЩюлкЪа

- здЖЏЛЏИпМЖЙЄГЬЪІ ЙуЖЋЪЁ/ЩюлкЪа

- ЙтЦїМўбаЗЂЙЄГЬЪІ ИЃНЈЪЁ/ИЃжнЪа

- ЯњЪлзмМрЃЈЙтЦїМўЃЉ ББОЉЪа/КЃЕэЧј

- МЄЙтЦїИпМЖЯњЪлОРэ ЩЯКЃЪа/КчПкЧј

- ЙтЦїМўЮяРэЙЄГЬЪІ ББОЉЪа/КЃЕэЧј

- МЄЙтбаЗЂЙЄГЬЪІ ББОЉЪа/В§ЦНЧј

- ММЪѕзЈМв ЙуЖЋЪЁ/НУХЪа

- ЗтзАЙЄГЬЪІ ББОЉЪа/КЃЕэЧј

- НсЙЙЙЄГЬЪІ ЙуЖЋЪЁ/ЩюлкЪа

ЗЂБэЦРТл

ЧыЪфШыЦРТлФкШн...

ЧыЪфШыЦРТл/ЦРТлГЄЖШ6~500Иізж

днЮоЦРТл

днЮоЦРТл